My code was wrong, but now it’s less wrong

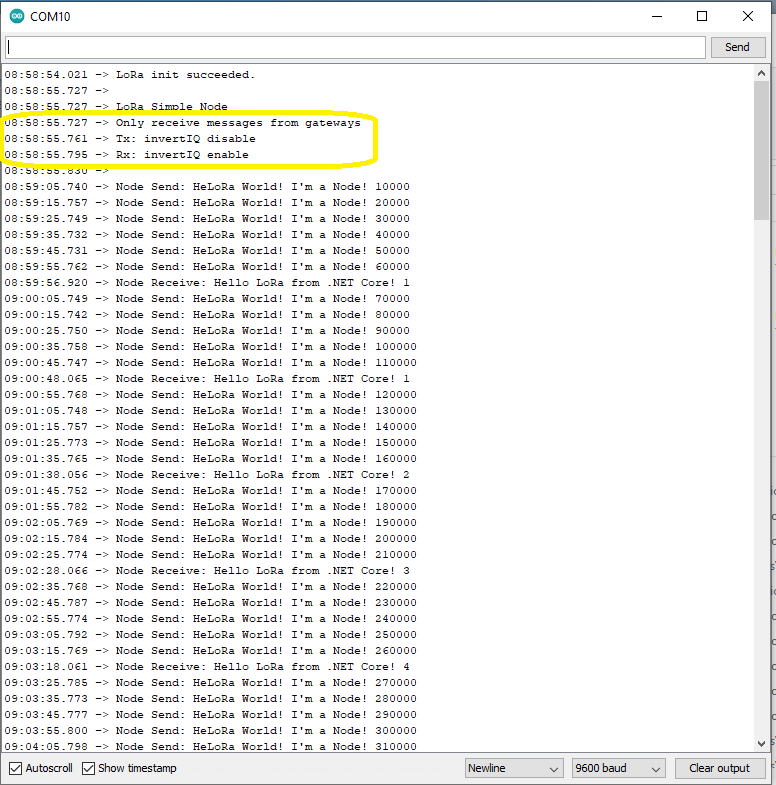

When I first fired up the my Seeeduino V4.2 + Dragino LoRa Shield using an application based on the Arduino-LoRa LoRaSimpleNode it didn’t work until in my library I set the sixth bit of RegInvertIQ to true.

The first issue was my RegInvertIQ register configuration code was wrong, it looks like I copied ‘n’ paste the code and forgot fix it up.

// RegDetectOptimize

if (detectionOptimize != RegDetectOptimizeDectionOptimizeDefault)

{

this.WriteByte((byte)Registers.RegDetectOptimize, (byte)detectionOptimize);

}

// RegInvertIQ

if (invertIQ != false)

{

this.WriteByte((byte)Registers.RegInvertIQ, (byte)detectionThreshold);

}

// RegSyncWordDefault

if (syncWord != RegSyncWordDefault)

{

this.WriteByte((byte)Registers.RegSyncWord, syncWord);

}

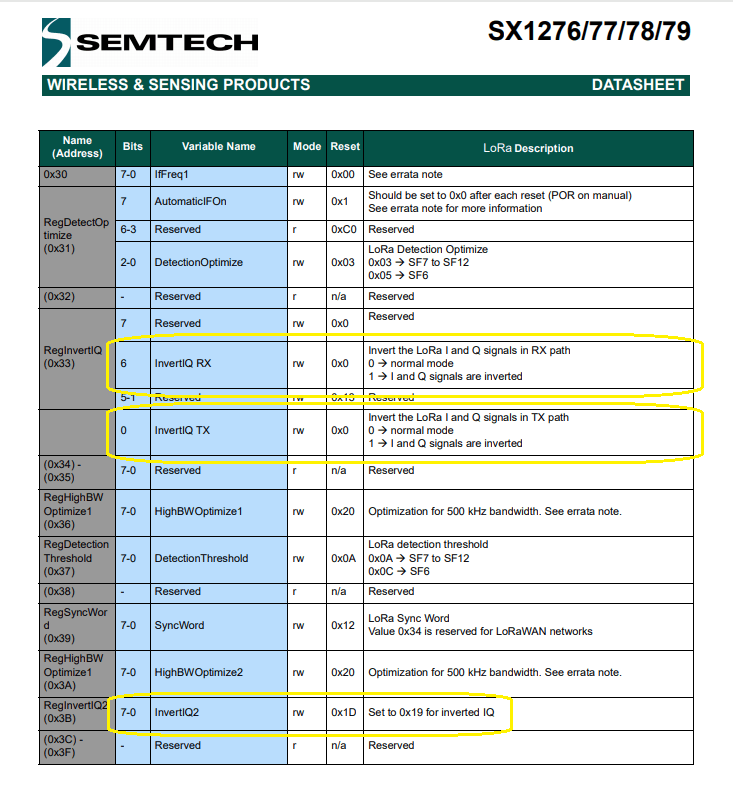

Even when I fixed up the code something still wasn’t quite right so I had a closer look at the SX127X datasheet and the LoRa-Arduino library code.

void LoRaClass::enableCrc()

{

writeRegister(REG_MODEM_CONFIG_2, readRegister(REG_MODEM_CONFIG_2) | 0x04);

}

void LoRaClass::disableCrc()

{

writeRegister(REG_MODEM_CONFIG_2, readRegister(REG_MODEM_CONFIG_2) & 0xfb);

}

void LoRaClass::enableInvertIQ()

{

writeRegister(REG_INVERTIQ, 0x66);

writeRegister(REG_INVERTIQ2, 0x19);

}

void LoRaClass::disableInvertIQ()

{

writeRegister(REG_INVERTIQ, 0x27);

writeRegister(REG_INVERTIQ2, 0x1d);

}

void LoRaClass::setOCP(uint8_t mA)

{

uint8_t ocpTrim = 27;

if (mA <= 120) {

ocpTrim = (mA - 45) / 5;

} else if (mA <=240) {

ocpTrim = (mA + 30) / 10;

}

In RegInvertIQ the sixth bit is the RX flag and the zeroth bit is the TX flag, in the enable method the zeroth bit was not set(even number) and in the disable method it was set (odd number). The enable and disable method were “inverting” both the TX and RX lines.

When I did a RegisterDump the initial value of RegInvertIQ was 0x27 which is a bit odd as datasheet indicated the default value of the zeroth bit is 0.

To double check I inspected the source of a couple of libraries including the ARM Lora-net/sx126x_driver: Driver for SX126x radio (github.com)

/*!

* RegDetectOptimize

*/

#define RFLR_DETECTIONOPTIMIZE_MASK 0xF8

#define RFLR_DETECTIONOPTIMIZE_SF7_TO_SF12 0x03 // Default

#define RFLR_DETECTIONOPTIMIZE_SF6 0x05

/*!

* RegInvertIQ

*/

#define RFLR_INVERTIQ_RX_MASK 0xBF

#define RFLR_INVERTIQ_RX_OFF 0x00

#define RFLR_INVERTIQ_RX_ON 0x40

#define RFLR_INVERTIQ_TX_MASK 0xFE

#define RFLR_INVERTIQ_TX_OFF 0x01

#define RFLR_INVERTIQ_TX_ON 0x00

/*!

* RegDetectionThreshold

*/

#define RFLR_DETECTIONTHRESH_SF7_TO_SF12 0x0A // Default

#define RFLR_DETECTIONTHRESH_SF6 0x0C

/*!

* RegInvertIQ2

*/

#define RFLR_INVERTIQ2_ON 0x19

#define RFLR_INVERTIQ2_OFF 0x1D

/*!

* RegDioMapping1

*/

case MODEM_LORA:

if (_rf_settings.lora.iq_inverted == true) {

write_to_register(REG_LR_INVERTIQ, ((read_register(REG_LR_INVERTIQ)

& RFLR_INVERTIQ_TX_MASK & RFLR_INVERTIQ_RX_MASK)

| RFLR_INVERTIQ_RX_ON | RFLR_INVERTIQ_TX_OFF));

write_to_register(REG_LR_INVERTIQ2, RFLR_INVERTIQ2_ON);

} else {

write_to_register(REG_LR_INVERTIQ, ((read_register(REG_LR_INVERTIQ)

& RFLR_INVERTIQ_TX_MASK & RFLR_INVERTIQ_RX_MASK)

| RFLR_INVERTIQ_RX_OFF | RFLR_INVERTIQ_TX_OFF));

write_to_register(REG_LR_INVERTIQ2, RFLR_INVERTIQ2_OFF);

}

Summary

My code supports the toggling of the RegInvertIQ “InvertIQ RX” and “InvertIQ TX” flags independently so users of the SX127X.NetCore library will need to pay attention to the configuration settings of the libraries used on other client devices.